# Chapter 8

# The Si surface and the Metal-Oxide-Semiconductor Structure

version 2.0 (updated: July 31, 2012), ©Prentice Hall

### Outline

- 8.1 The semiconductor surface

- 8.2 The ideal Metal-Oxide-Semiconductor structure

- 8.3 The ideal Metal-Oxide-Semiconductor structure at zero bias

- 8.3.1 General relations for the electrostatics of the ideal MOS structure

- 8.3.2 Electrostatics of the MOS structure under zero bias

- 8.4 The ideal Metal-Oxide-Semiconductor structure under bias

- 8.4.1 Depletion

- 8.4.2 Flatband

- 8.4.3 Accumulation

- 8.4.4 Threshold

- 8.4.5 Inversion

- 8.4.6 Summary of charge-voltage characteristics

- 8.5 Dynamics of the MOS structure

- 8.5.1 Quasi-static C-V characteristics

- 8.5.2 High-frequency C-V characteristics

- 8.5.3 Deep depletion

- 8.6 Weak inversion and the subthreshold regime

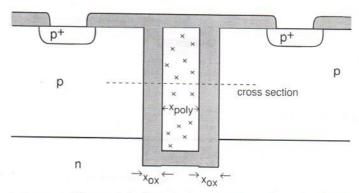

- 8.7 Three-terminal MOS structure

- 8.8 Summary

- 8.9 Further reading

### Advanced Topics

- AT8.1 Poisson-Boltzmann formulation of MOS electrostatics

- AT8.1.1 Approximations for depletion

- AT8.1.2 Approximations for accumulation

- AT8.1.3 Approximations for inversion

## Problems

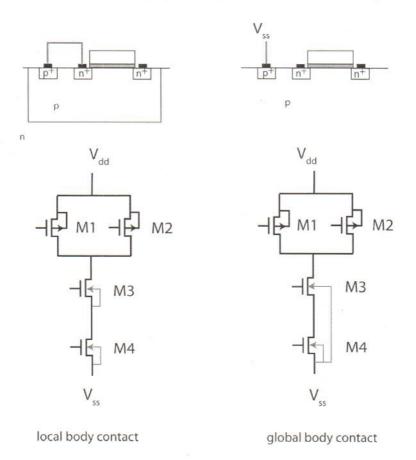

This chapter deals with what is perhaps the most important material system in modern microelectronics: the metal-oxide-semiconductor structure or MOS. The MOS structure is at the heart of integrated microelectronics. A basic CMOS inverter is made out of two metal-oxide-semiconductor field-effect transistors (MOSFETs) in which carrier transport is controlled by the field-effect action of a MOS structure. Hundreds of millions of them are now integrated together on a single chip. MOS capacitors are also the storage element of Dynamic Random-Access Memories (DRAM). Billions of them are routinely integrated on a memory chip. MOS structures also appear when interconnect metal lines run over an oxide-covered semiconductor surface. In a typical modern microprocessor, there are tens of meters worth of them.

In spite of its seemingly restrictive name, the MOS structure is to be viewed here as a generic sandwich of a highly-conducting material on top of an insulator, all on top of a semiconductor (a better term might be MIS, for Metal-Insulator-Semiconductor). The treatment of the MOS structure presented in this chapter can be easily extended to heavily-doped polysilicon gates which are the preferred choice in modern CMOS. Similarly, insulators other than silicon dioxide are widely used in modern microelectronics. A prominent example is Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>). With some precautions, the MOS theory can be used to treat MIS structures based on semiconductors other than Si and in which the "insulator" is actually a wide bandgap semiconductor. A prominent example is the metal/AlGaAs/InGaAs heterostructure at the heart of modern High Electron Mobility Transistors (HEMTs).

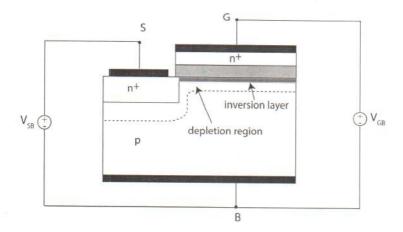

The goal of this chapter is to understand the changes brought to the electrostatics of the MOS structure upon the application of a voltage to the metal with respect to the semiconductor. Even though current cannot flow through the insulator, the charge distribution in the semiconductor close to the insulator/semiconductor interface is affected in a major way. One can induce a depletion region, accumulate majority carriers, or all together "invert" the semiconductor type and create a thin layer of minority carriers. This "inversion layer" constitutes the conducting channel in most MOSFETs.

An additional goal of this chapter is to continue building up the tool kit for studying semiconductor devices by introducing the Poisson-Boltzmann formulation. This is a powerful formalism to rigorously analyze the electrostatics of the MOS structure. The usefulness of the Poisson-Boltzmann formulation transcends this structure as it can be applied to other junctions that appear in semiconductor devices.

This chapter places special emphasis in the understanding of the capacitance-voltage characteristics of the MOS structure. As in the metal-semiconductor and PN junctions, the C-V characteristics summarize in a compact way the electrostatics of the structure. C-V characteristics form also the basis for a variety of techniques to characterize and diagnose semiconductor surfaces, interfaces, dielectrics and devices.

This is one of the most important chapters in this book. Solid command of the physics of the MOS structure is essential to understand MOSFETs and CMOS.

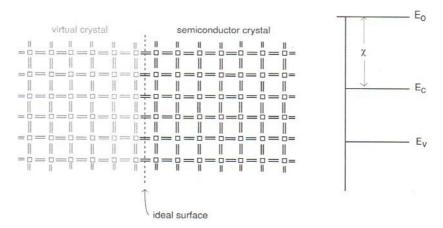

Figure 8.1: Left: Schematic diagram of an ideal surface with unperturbed semiconductor bonds. This is as if the real crystal continued into a "virtual crystal" where carriers are forbidden. Right: energy band diagram in the vicinity of an ideal surface. The bands are "bulk-like" all the way to the surface.

# 8.1 The semiconductor surface

At a semiconductor surface, the perfect crystalline periodicity of the solid comes to an abrupt end. This affects the transport properties of electrons and holes in its vicinity in a major way. Providing a simple and intuitive picture of what happens at a surface is the goal of this section. Before we do that, let us introduce the concept of *ideal semiconductor surface*.

An "ideal surface" can be thought of as one in which the semiconductor lattice comes to an end but the bulk electronic properties are unmodified by this disruption. Schematically, we can visualize an ideal surface if we introduce an imaginary plane inside the bulk of a semiconductor that carriers cannot traverse. This is illustrated on the left of Fig. 8.1. On one side is the real crystal, on the other side is a "virtual" crystal. Along the ideal surface plane, the semiconductor bonding arrangement remains undisturbed. Carriers can come up to that plane without feeling its presence in any way. They just simply cannot cross it because there are no allowed states on the other side of the interface for the carriers to go to. Another view of this situation is to consider that a large energy barrier exists right at the surface, as sketched on the right of Fig. 8.1. The barrier height for electrons in the conduction band is equal to the electron affinity of the semiconductor. It is even higher for the holes. As a consequence, the hole and electron current components normal to that plane are both zero. This concept of an ideal surface, while naive, is useful. We already encountered it in our discussion on the metal-semiconductor junction. We will invoke it many more times in this book.

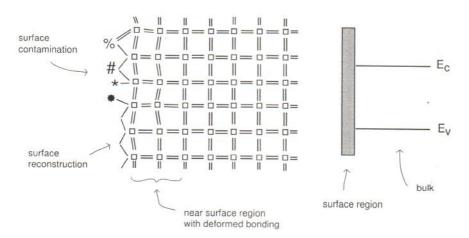

In a "real" surface the four-fold coordination of the semiconductor atoms cannot be preserved. Even if nothing else happens, unsatisfied bonds will be present. This is a rather unstable situation as the atoms are eager to lower their energy by attempting to emulate four-fold coordination. As a consequence, a surface with unsatisfied bonds is very reactive. The surface atoms can find various ways to lower their total energy, as schematically illustrated in Fig. 8.2. One of them is to bond with foreign atoms or molecules, such as O or C or organic contaminants, that might

Figure 8.2: Left: Schematic illustration of a "real" surface with surface contaminants, surface reconstruction, and a subsurface region with deformed bonding. Right: Schematic energy band diagram in the vicinity of a "real" surface" showing a different electron energy distribution near the surface.

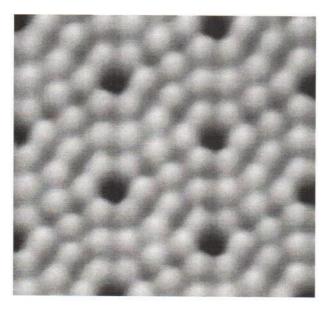

Figure 8.3: Scanning Tunneling Microscope picture of the 7x7 reconstruction of the (111) Si surface. Each round gray feature is associated with one distinct Si atom. The peculiar atomic arrangement pattern that is observed arises from minimization of the surface energy [courtesy of R. Martel and Ph. Avouris, IBM].

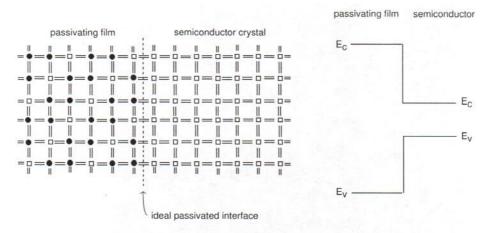

Figure 8.4: Left: Schematic illustration of surface passivation. A dielectric film has been placed on top of the semiconductor surface so that bulk-like bonding exists at the dielectric/semiconductor interface. Right: Energy band diagram in the vicinity of a passivated interface. The bands in the semiconductor are "bulk-like" all the way to the interface.

be present in the atmosphere surrounding the surface. A semiconductor surface, if exposed to air, oxidizes and gets contaminated very easily. A second avenue for surface energy lowering is *surface reconstruction* in which the surface atoms bond among themselves in an arrangement that is rather different from the one in the bulk. A (111) Si surface, for example, reconstructs itself into a spectacular diamond-shape 7x7 arrangement, pictured in Fig. 8.3.

When considering the impact that a "real" surface has on semiconductor device behavior, we might be tempted to believe that whatever it is, it should be confined to the immediate vicinity of the surface, that is the region where the semiconductor bonding is upset from its bulk arrangement. This deformed region is actually very thin, perhaps two or three monolayers. In consequence, we might be lead to believe that the influence of the surface does not extend more than a few nanometers below the surface. From a crystalline point of view, this argument is true, but from an electrostatic and transport one, it is not. We will learn in this chapter that a surface can modify the electrostatics of the bulk underneath to distances that can be as high as a few microns. Furthermore, we already saw in Ch. 5 that in minority carrier type situations the influence of surface recombination reaches several diffusion lengths into the bulk. Depending on doping level and processing details, this can be as far as hundreds of microns.

The high reactivity of an exposed semiconductor surface makes it unsuitable for semiconductor device applications. The microelectronics revolution would have not taken place without the discovery of <u>surface passivation</u>. This consists of the deposition of a dielectric material or the formation of a thin-film on top of a semiconductor surface such that bulk-like bonding at the interface is preserved. This is schematically illustrated in Fig. 8.4.

The most important passivating film is SiO<sub>2</sub>. When Si is oxidized in an ultraclean environment, Si reacts with O to form SiO<sub>2</sub>, which grows on the Si surface. SiO<sub>2</sub> formed this way is an amorphous dielectric material with remarkable properties. One of them is that at the Si-SiO<sub>2</sub> interface, nearly all Si bonds are satisfied. If the black circles are taken as the O atoms, Fig. 8.4

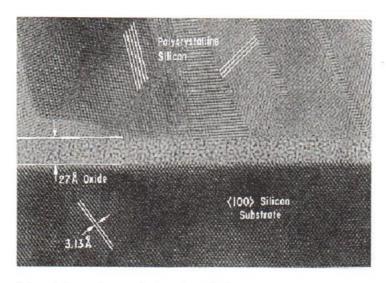

Figure 8.5: Transmission electron micrograph of modern MOS structure showing 1-2 monolayer surface roughness at the Si-SiO<sub>2</sub> interface. The gate, made out of heavily-doped polysilicon, shows several grains with different orientations. The extraordinary resolution of this picture permits the direct observation of the lattice planes that provides an absolute length calibration [courtesy of D. Buchanan, IBM].

can be interpreted as an ideal SiO<sub>2</sub> film on a Si surface. Notice that there are twice as many O atoms as Si atoms (the open squares) in the dielectric film. Note also that all atoms in the dielectric as well as at the dielectric/semiconductor interface share a total of eight valence electrons, the ideal bonding configuration.

This simple picture is however misleading in at least two important ways. First,  $SiO_2$  films used in microelectronics are amorphous, that is, they do not have the long-range crystalline order that is suggested in Fig. 8.4. There is some short-range order, to be sure, with a bonding configuration similar to the one implied in this figure, but the film is really made out of multiple tiny crystallites with all kinds of orientations. A second problem is that Fig. 8.4 suggests that the Si/SiO<sub>2</sub> interface is perfectly flat. This is also not the case. Even carefully prepared interfaces have surface roughness on the scale of one to two monolayers. This is seen in the transmissionelectron microscope picture of Fig. 8.5 that shows a cross section of a MOS structure used in modern CMOS applications. The MOS structure of the picture has a polysilicon gate on top of a 2.7 nm thick SiO<sub>2</sub> layer grown on a (100) Si substrate. If one looks in detail, one can see an Si/SiO<sub>2</sub> interface that is not flat but exhibits a roughness of about two monolayers. Surface roughness has very important implications for carrier transport along the Si/SiO2 interface, as it happens in a MOSFET. This will be explored in Ch. 10. Interestingly, the extraordinary resolution of the picture in Fig. 8.5 allows the direct observation of the lattice planes in the Si substrate. This provides an absolute length calibration for the picture. Also, the polycrystalline nature of the gate is apparent.

In an ideal surface, the energy band diagram is bulk-like all the way to the surface, as sketched on the right of Fig. 8.1. The electrons do not "fall off" the semiconductor at the surface because they face an energy barrier equal to the electron affinity of the semiconductor. Electrons need to have an energy equal to the vacuum energy to escape from the semiconductor.

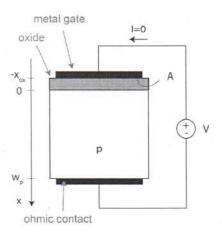

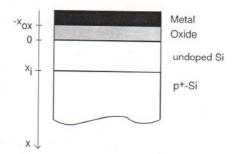

Figure 8.6: Sketch of ideal MOS structure on p-type substrate.

The energy band diagram of a perfectly passivated semiconductor surface is similar to an ideal surface, *i.e.*, the semiconductor bands remain bulk-like all the way to the interface. As we discussed in Ch. 1, the band diagram of an insulator is qualitatively identical to that of a semiconductor, except that the bandgap is much wider. The bandgap of  $SiO_2$ , for example, is about 9 eV. In consequence, at the insulator/semiconductor interface, there is a large discontinuity in the conduction band and the valence bands that prevents carriers from escaping. This is shown on the right of Fig. 8.4.

The energy band description of the bulk semiconductor is inappropriate in the vicinity of an unpassivated surface. The particular bonding arrangement of the surface and the presence of contamination results in an electron state configuration that is rather different from the one that prevails in the bulk. More importantly, the existence of a bandgap devoid of electron states can no longer be guaranteed, and in fact, a general continuum of states is more appropriate. This is pictured on the right of Fig. 8.2.

## 8.2 The ideal Metal-Oxide-Semiconductor structure

As in the case of the PN diode and the Schottky diode, it is useful to define the concept of an "ideal MOS structure". This captures the essence of the MOS physics while hiding some of the second-order effects. Later in this chapter, we will relax some of the assumptions made in this section.

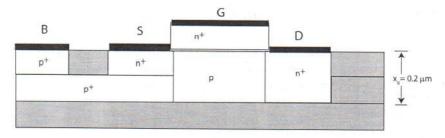

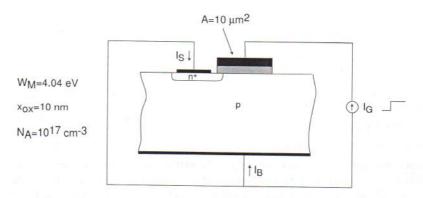

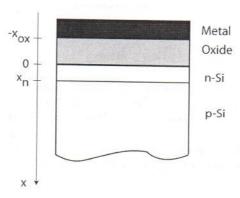

A sketch of an ideal MOS structure is shown in Fig. 8.6. It consists of a p-type semiconductor (one can equally define it on an n-type substrate), an oxide of thickness  $x_{ox}$ , and a metal film. the metal is referred to this as the "gate". The semiconductor is contacted at the bottom by an ideal ohmic contact.

The following assumptions characterize the ideal MOS structure:

- This is a one dimensional situation. There are no 2D or 3D effects.

- We assume an ideal semiconductor surface at the oxide-semiconductor interface, i.e., smooth and defect free.

- The doping level in the semiconductor is uniform throughout.

- We assume that the metal work function and the doping level in the semiconductor are such that under zero bias, there is a depletion region in the semiconductor.

- In situations in which there is a depletion region in the semiconductor, we treat it under the depletion approximation.

- Under the application of a DC voltage, we assume that no DC current flows.

- The semiconductor is contacted through an ideal ohmic contact, as defined earlier in this book.

- We neglect any sidewall effects associated with the edges of the device.

- Maxwell-Boltzmann statistics apply to both types of carriers under all conditions.

Fig. 8.6 also defines the axis that we will use in our analysis. The origin is placed at the oxide/semiconductor interface. The area of the MOS structure is A. The voltage convention that we will follow is also shown in the figure. For a MOS structure on a p-type substrate, V is defined as the potential difference between the gate and the semiconductor.

# 8.3 The ideal Metal-Oxide-Semiconductor structure at zero bias

We start by analyzing the MOS structure at zero bias. The first question that one might ask is why do we use this notation, "zero bias," as opposed to "thermal equilibrium" used earlier in this book. Is it the same?

In an ideal MOS structure with a perfectly insulating oxide, no electron flow can take place between the metal and the semiconductor and the system cannot really attain thermal equilibrium. We can deal with this problem by shorting together the metal and the semiconductor through an external wire so that electron redistribution can take place through it. This is equivalent to applying a zero bias across the structure.

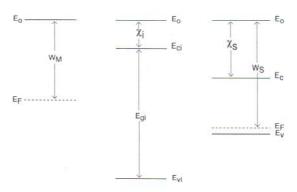

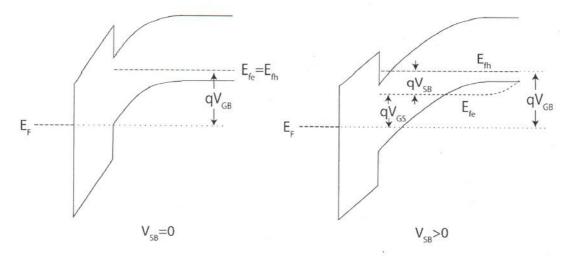

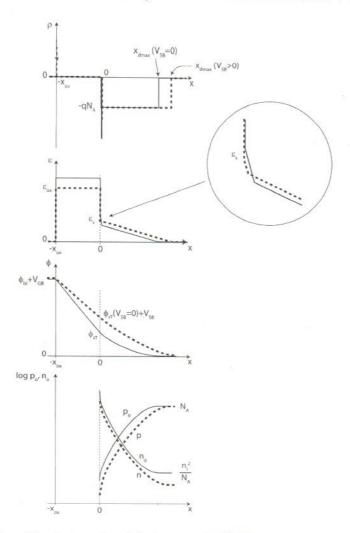

Consider a metal/oxide/p-type semiconductor structure with the three materials far apart, as sketched in an energy band diagram in Fig. 8.7a (dual situations occur with an n-type semiconductor substrate, as we will summarize later). The common reference energy for the three band diagrams is the vacuum level. The electronic structure of the metal is characterized by its work function. The semiconductor and the insulator are characterized by their electron affinity and their bandgaps, as well as the location of the Fermi level. In the case of the semiconductor, the Fermi level is set by doping. For the insulator, in principle one could establish the location

a) metal, insulator and semiconductor far apart

b) metal, insulator and semiconductor in intimate contact

Figure 8.7: Energy band diagrams a) for isolated metal, insulator and semiconductor, and b) after bringing them in intimate contact at zero bias.

of the Fermi level as if it was an intrinsic semiconductor. In practice, the bandgap of the insulator is so large, that the Fermi level can swing widely through most of it without changing in any significant way the occupation of the bands. For all practical purposes, the valence band is always completely full of electrons and the conduction band is perfectly empty. Because of this, the Fermi level is not usually drawn inside an insulator.

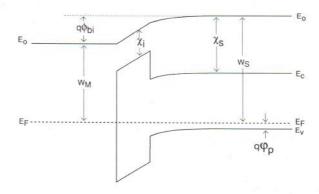

The situation shown in Fig. 8.7a is one in which the Fermi level in the semiconductor is lower than in the metal. In consequence, if these three materials are brought in intimate contact through an external wire, electrons will tend to flow from the metal to the semiconductor. When this happens, the metal becomes positively charged and the semiconductor acquires negative charge. This sets up an electric field that eventually brings carrier exchange to a halt establishing thermal equilibrium. The bottom of Fig. 8.7 shows the resulting energy band diagram at zero bias.

There are several interesting features in this energy band diagram. First of all, far away from their interfaces with the insulator, bulk thermal equilibrium conditions prevail in the metal and the semiconductor. In the vicinity of the oxide/semiconductor interface, the charge exchange

that has taken place between the metal and the semiconductor implies that the band diagram of the semiconductor bends down. In addition to getting more electrons close to the insulator, thermal equilibrium demands that fewer holes are present there. The semiconductor has become negatively charged. In fact, from a charge point of view, since holes are the majority carriers, the reduction of the hole concentration is far more significant than the increase of the electron concentration. The net effect, in any case, is that the semiconductor is negatively charged in the neighborhood of the interface with the insulator. This negative charge is imaged at the metal-insulator interface where there is a deficit of electrons. In the length scale of interest, this does not bend the band diagram of the metal in a significant way and it is not shown (refer to a related discussion in Section 7.2).

The dipole of charge that has appeared across the MOS structure results in two features in the band diagram. First, it bends the bands in the insulator. The fact that there is not bulk charge inside an ideal insulator implies that the bands are inclined but straight. Second, there is a built-in potential difference across the entire structure. As in previous junctions of dissimilar materials, the built-in potential is entirely set by the work functions of the end materials. In this case, it is given by:

$$q\phi_{bi} = W_S - W_M \tag{8.1}$$

A final observation to be made about the energy band diagram of Fig. 8.7 is the appearance of large conduction band and valence band discontinuities at the semiconductor/insulator interface. They constitute huge energy barriers to carrier flow and ideally prevent the injection of electrons and holes from the semiconductor to the insulator.

Before we proceed to analyze in detail the electrostatics of this situation, let us first derive some general relationships for the electrostatics of the MOS structure. We will derive them at zero bias, but with suitable modification they can also be used under bias.

## 8.3.1 General relations for the electrostatics of the ideal MOS structure

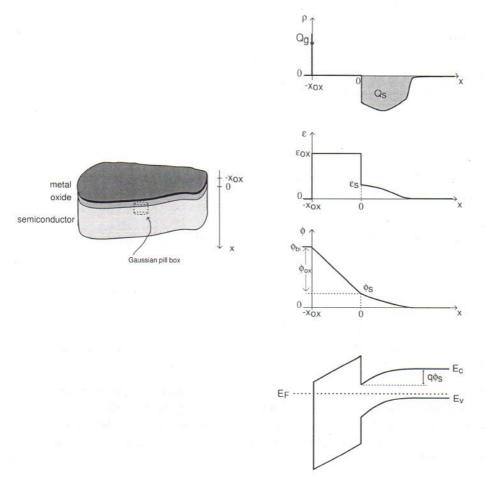

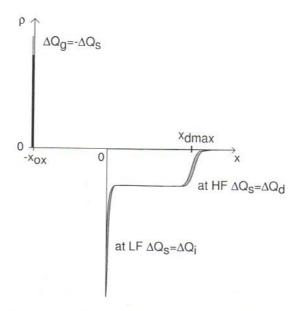

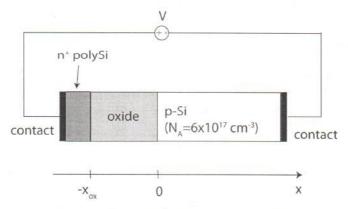

Fig. 8.8 shows a general MOS structure at zero bias. The coordinate system is selected to point into the wafer, with the origin placed at the semiconductor/insulator interface, as sketched on the left of Fig. 8.8. The right of the figure shows the volume charge density, the electric field, and the electrostatic potential along the space coordinate x.

The top of Fig. 8.8 shows the charge distribution in space. In the semiconductor we depict a generic charge distribution that extends to some depth from the  $\mathrm{Si/SiO_2}$  interface and that integrates to a total charge areal density  $Q_s$  (in units of  $C/cm^2$ ). The insulator is assumed to be ideal and devoid of any charge inside. The metal also rejects volume charge but allows it at its surfaces. We can think of this charge as a "sheet" located at the metal-oxide interface with an areal density  $Q_g$  (in units of  $C/cm^2$ ). Overall charge neutrality demands that:

$$Q_g = -Q_s \tag{8.2}$$

Figure 8.8: Schematic of MOS structure defining the coordinate axis and a Gaussian pill box (left). Generic sketches of, from top to bottom, volume charge density, electric field, electrostatic potential end energy band diagram for the MOS structure (right).

The field lines produced by this dipole of charge originate in the sheet charge at the metal/insulator interface and terminate in the semiconductor. As a result, the field inside the metal as well as sufficiently deep inside the semiconductor are zero. Application of Gauss law to this situation is straightforward. If we construct a "pill box" that includes all  $Q_s$  and penetrates partially into the oxide, as shown on the left of Fig. 8.8, we find the electric field in the oxide to be:

$$\mathcal{E}_{ox} = -\frac{Q_s}{\epsilon_{ox}} \tag{8.3}$$

where  $\epsilon_{ox}$  is the permittivity of the oxide <sup>1</sup>.  $\mathcal{E}_{ox}$  is uniform in space inside the oxide since there

<sup>&</sup>lt;sup>1</sup>It is important to keep in mind the distinction between permittivity ( $\epsilon$ , in  $F/cm^2$ ) and dielectric constant ( $\kappa$ , no units). They are related through  $\epsilon = \kappa \epsilon_o$  where  $\epsilon_o$  is the permittivity of vacuum (value given in Appendix A).

are no charges there.

The permittivities of the insulator and the semiconductor are generally different. This implies that at the Si/insulator interface, the electric field is discontinuous. The relationship between the normal components of the electric field on both sides of the interface is obtained from the continuity of the electric displacement vector, that is:

$$\epsilon_s \mathcal{E}_s = \epsilon_{ox} \mathcal{E}_{ox} \tag{8.4}$$

The permittivity of SiO<sub>2</sub> is 3.9. This is exactly three times smaller than the permittivity of Si (see Appendix B). Therefore, the field inside the oxide is three times the field at the semiconductor surface.

Substituting Eq. 8.4 into 8.3 provides a relationship between the electric field at the semiconductor/insulator interface on the semiconductor side and  $Q_s$ :

$$\mathcal{E}_s = -\frac{Q_s}{\epsilon_s} \tag{8.5}$$

We could have obtained this result by selecting a different pillbox that includes all of  $Q_s$  and has one of its surfaces placed exactly at x = 0.

The electric field distribution results in an electrostatic potential profile that is sketched in Fig. 8.8. In this graph, the origin of potentials is selected deep in the bulk of the semiconductor. The total potential difference across the structure at zero bias is  $\phi_{bi}$ . The total potential drop across the structure is equal to the sum of the drop in the semiconductor,  $\phi_s$ , plus the drop in the insulator,  $\phi_{ox}$ , that is:

$$\phi_{bi} = \phi_s + \phi_{ox} \tag{8.6}$$

$\phi_s$  is called the *surface potential*. It is related to the detailed charge distribution in space inside the semiconductor.  $\phi_{ox}$  is the potential build-up across the insulator. Since the field in the oxide is uniform,  $\phi_{ox}$  is given by:

$$\phi_{ox} = x_{ox} \mathcal{E}_{ox} \tag{8.7}$$

Eq. 8.6 is the basis for a general relationship between  $\phi_s$  and  $Q_s$ . Towards deriving this, let us first define the capacitance per unit area of the insulator:

$$C_{ox} = \frac{\epsilon_{ox}}{x_{ox}} \tag{8.8}$$

If we now plug Eq. 8.7 into Eq. 8.6 and use Eqs. 8.4 and 8.5, we can write:

$$\phi_{bi} = \phi_s - \frac{Q_s}{C_{ox}} \tag{8.9}$$

The relationships just derived apply to any ideal MOS structure under any circumstances. They have been obtained from fundamental statements about the electrostatics of the structure. In particular, they all apply to situations under bias if we substitute  $\phi_{bi}$  by the appropriate expression for the total potential build-up across the structure.

The bottom sketch in Fig. 8.8 is the energy band diagram. A significant point to be made is that with the electrostatic potential reference that was selected above, the total band bending inside the semiconductor is given by  $q\phi_s$ .

We can now proceed to study in some detail the electrostatics of the zero-bias situation outlined above.

**Exercise 8.1:** A certain MOS structure with  $x_{ox} = 4.5 \text{ nm}$  exhibits  $\phi_{bi} = 1 \text{ V}$  and  $\phi_{ox} = 0.42 \text{ V}$  at zero bias. Calculate  $\phi_s$ ,  $Q_s$ ,  $\mathcal{E}_s$ , and  $\mathcal{E}_{ox}$ .

There are multiple ways to go about solving this problem. We can use Eq. 8.7 to get  $\mathcal{E}_{ox}$ :

$$\mathcal{E}_{ox} = \frac{\phi_{ox}}{x_{ox}} = \frac{0.42 \ V}{4.5 \times 10^{-7} \ cm} = 9.3 \times 10^5 \ V/cm$$

From here, we can calculate  $\mathcal{E}_s$  using Eq. 8.4:

$$\mathcal{E}_s = \frac{\epsilon_{ox}}{\epsilon_s} \mathcal{E}_{ox} = 0.33 \times 9.3 \times 10^5 \ V/cm = 3.1 \times 10^5 \ V/cm$$

We can get  $Q_s$  from either Eq. 8.3 or 8.5. Using the later one:

$$Q_s = \epsilon_s \mathcal{E}_s = 11.7 \times 8.85 \times 10^{-14} F/cm \times 3.1 \times 10^5 \ V/cm = 3.2 \times 10^{-7} \ C/cm^2$$

Finally,  $\phi_s$  can be obtained from Eq. 8.6:

$$\phi_s = \phi_{bi} - \phi_{ox} = 0.58 V$$

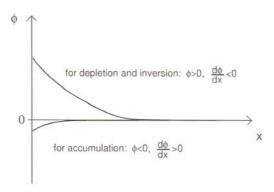

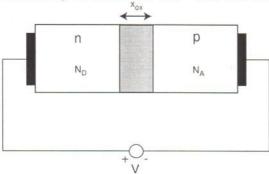

## 8.3.2 Electrostatic of the MOS structure under zero bias

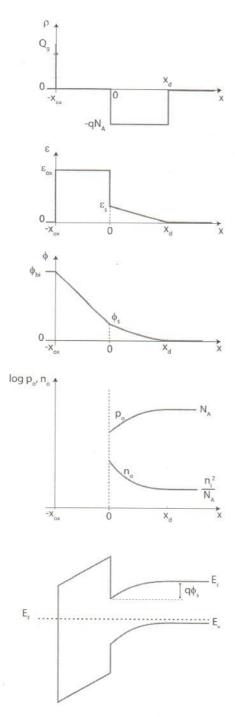

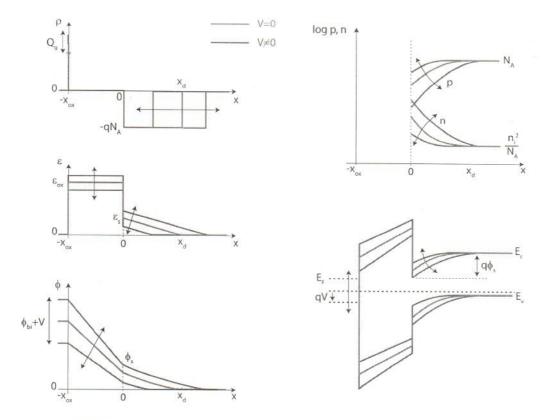

For a uniformly-doped semiconductor, deriving an analytical formulation of the electrostatics of the MOS structure under zero bias is relatively straightforward under the depletion approximation. If one focuses on the semiconductor in Fig. 8.7, one sees that close to the interface with the insulator there is a region with a space charge region, while far away from it, the bulk is quasineutral. This is similar to the situations that we observed in the PN diode and the Schottky diode. Consistent with the treatment that was followed there, we can perform the depletion approximation and assume that up to a certain depth,  $x_d$ , the semiconductor is devoid of majority carriers (holes in this case) and beyond  $x_d$ , the semiconductor is perfectly neutral. Under this approximation, the volume charge density, electric field, electrostatic potential and equilibrium carrier concentrations and energy band diagram of Fig. 8.9 result.

Figure 8.9: From top to bottom: sketches of volume charge density, electric field, electrostatic potential, equilibrium carrier concentration and energy band diagram in a MOS structure under zero bias under the depletion approximation (p-substrate).

Within the depletion approximation, the volume charge density inside the depletion region is uniform and equal to  $\rho = -qN_A$ . Hence, the integrated semiconductor charge is:

$$Q_s \simeq -qN_A x_d \tag{8.10}$$

The electric field distribution in the semiconductor has a triangular shape with a maximum at the semiconductor interface with the oxide. Plugging Eq. 8.10 into Eq. 8.5, the electric field at the semiconductor surface is given by:

$$\mathcal{E}_s \simeq \frac{qN_A x_d}{\epsilon_s} \tag{8.11}$$

Eq. 8.3 gives an expression that allows the calculation of the electric field inside the oxide. We can then write:

$$\mathcal{E}_{ox} \simeq \frac{qN_A x_d}{\epsilon_{ox}} \tag{8.12}$$

The electrostatic potential in the semiconductor has a parabolic shape. The surface potential is obtained by integrating the triangularly shaped electric field. This yields:

$$\phi_s \simeq \frac{qN_A x_d^2}{2\epsilon_s} \tag{8.13}$$

The only unknown at this time is the depth of the depletion region  $x_d$ . This can be obtained by plugging Eqs. 8.13 and 8.10 into the fundamental electrostatics relation 8.9 to yield:

$$\phi_{bi} \simeq \frac{qN_A x_d^2}{2\epsilon_s} + \frac{qN_A x_d}{C_{ox}} \tag{8.14}$$

Solving this quadratic equation we obtain:

$$x_d \simeq \frac{\epsilon_s}{C_{ox}} \left( \sqrt{1 + \frac{4\phi_{bi}}{\gamma^2} - 1} \right) \tag{8.15}$$

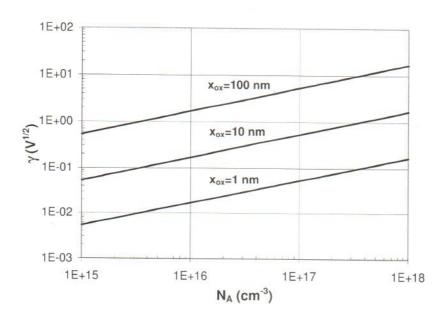

where  $\gamma$  is the so-called body factor coefficient:

$$\gamma = \frac{1}{C_{ox}} \sqrt{2\epsilon_s q N_A} \tag{8.16}$$

which has units of  $V^{1/2}$ . Eq. 8.15 states that the larger the difference in work functions between the metal and the semiconductor, the larger  $x_d$  is. This makes sense since the higher  $\phi_{bi}$ , the larger the charge exchange that needs to take place.

Figure 8.10: Body factor coefficient, γ, vs. substrate doping level for different values of the SiO<sub>2</sub> thicknesses.

It is also of interest to focus on the total charge in the depletion layer. This is given by:

$$Q_d \simeq -qN_A x_d \simeq -\sqrt{2\epsilon_s q N_A \phi_s} \tag{8.17}$$

where we have used Eq. 8.13. As in a PN junction and a Schottky junction, there is a square-root relationship between depletion charge and potential build up across a depletion region.

$\gamma$  is an important parameter of a MOS structure. As Eq. 8.16 indicates,  $\gamma$  depends on the doping level of the substrate and the capacitance per unit area of the insulator. As it will be better understood later on in this chapter,  $\gamma$  makes a statement about the relative magnitude of the depletion region capacitance to the oxide capacitance. The higher the doping level, the thinner the depletion region in the semiconductor and the higher the depletion capacitance, hence  $\gamma$  goes up. Similarly, the thinner the oxide, the higher the oxide capacitance and the lower  $\gamma$  gets. Both dependencies are seen in Fig. 8.10 which graphs  $\gamma$  vs.  $N_A$  and the SiO<sub>2</sub> thickness.

In a well designed MOSFETs, a proper balance between the oxide and depletion region thicknesses is required. Hence,  $\gamma$  is typically on the order of 0.1 to 1  $V^{1/2}$ . In time,  $\gamma$  has tended to decrease as MOSFET size has shrunk.

Once the electrostatic potential in the semiconductor is known, it is straightforward to obtain first-order expressions for the zero bias carrier densities in the semiconductor. The procedure is

identical to that one followed in the case of the metal-semiconductor junction in Section 7.2.3.

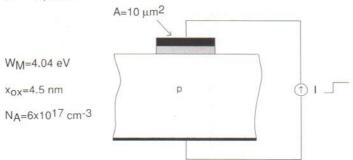

Exercise 8.2: Consider a MOS structure made out of a W gate ( $W_M = 4.54 \text{ eV}$ ), a 4.5 nm SiO<sub>2</sub> insulator, and a p-type doped Si substrate with  $N_A = 6 \times 10^{17} \text{ cm}^{-3}$ . Estimate the electric field in the oxide and the surface potential at zero bias.

Since  $W_M$  is about  $\chi + E_g/2$ , this structure is likely to be in depletion. In order to compute  $\mathcal{E}_{ox}$ , we first need to calculate  $x_d$ . Before that we need to compute  $\phi_{bi}$ ,  $C_{ox}$  and  $\gamma$ , which can be obtained, respectively, from Eqs. 8.1, 8.8 and Eq. 8.16. In order to get  $\phi_{bi}$ , we need to first compute  $W_S$ :

$$W_S = \chi + E_g + kT \ln \frac{N_A}{N_v} = 4.04 + 1.12 + 0.026 \times \ln \frac{6 \times 10^{17}}{3.1 \times 10^{19}} = 5.06 \ eV$$

Now:

$$\phi_{bi} = \frac{1}{q}(W_S - W_M) = 5.06 - 4.54 = 0.52 V$$

$$C_{ox} = \frac{\epsilon_{ox}}{x_{ox}} = \frac{3.45 \times 10^{-13} \ F/cm}{4.5 \times 10^{-7} \ cm} = 7.7 \times 10^{-7} \ F/cm^2$$

$$\gamma = \frac{1}{C_{ox}} \sqrt{2\epsilon_s q N_A} = \frac{\sqrt{2 \times 1.04 \times 10^{-12} \ F/cm \times 1.6 \times 10^{-19} \ C \times 6 \times 10^{17} \ cm^{-3}}}{7.7 \times 10^{-7} \ F/cm^2} = 0.58 \ V^{1/2}$$

We can now use Eq. 8.15 to obtain  $x_d$ :

$$x_d = \frac{\epsilon_s}{C_{ox}} (\sqrt{1 + \frac{4\phi_{bi}}{\gamma^2}} - 1) = \frac{1.04 \times 10^{-12} \; F/cm}{7.7 \times 10^{-7} \; F/cm^2} (\sqrt{1 + \frac{4 \times 0.52 \; V}{0.58^2 \; V}} - 1) = 2.3 \times 10^{-6} \; cm = 23 \; nm)$$

$\mathcal{E}_{ox}$  can now be obtained using Eq. 8.12:

$$\mathcal{E}_{ox} = \frac{qN_Ax_d}{\epsilon_{ox}} = \frac{1.6\times 10^{-19}~C\times 6\times 10^{17}~cm^{-3}\times 2.3\times 10^{-6}~cm}{3.45\times 10^{-13}~F/cm} = 6.4\times 10^5~V/cm$$

The surface potential can be obtained from Eq. 8.13:

$$\phi_s = \frac{qN_Ax_d^2}{2\epsilon_s} = \frac{1.6\times 10^{-19}~C\times 6\times 10^{17}~cm^{-3}\times (2.3\times 10^{-6}~cm)^2}{2\times 1.04\times 10^{-12}~F/cm} = 0.24~V$$

In the next section we will learn how to confirm that indeed this structure is in depletion.

# 8.4 The ideal Metal-Oxide Semiconductor structure under bias

The application of a voltage to the gate with respect to the body of a MOS structure affects the potential and charge distributions throughout. For the case of a p-type substrate, if we define as positive the voltage in the metal with respect to the semiconductor, the total potential difference across the structure goes from a zero bias value of  $\phi_{bi}$  to a new value equal to  $\phi_{bi} + V$ , where V

is the applied voltage. The charge dipole across the MOS structure has to adapt itself so as to produce such a potential build up. In what way is it modified and what are the consequences of this? These are the topics that we study in this section.

Before discussing the details, we need to recognize that the presence of the oxide in the MOS structure blocks the flow of current even when a voltage is applied. Current continuity then implies that no current flows across the semiconductor. So, even though a bias has been applied, the semiconductor remains in a quasi-equilibrium condition. We can therefore conclude that similar to the PN diode or the Schottky diode, the electrostatics of a MOS structure with a built-in potential  $\phi_{bi}$  under a voltage V are identical to the electrostatics of a MOS structure with a built-in potential equivalent to  $\phi_{bi} + V$  under zero bias<sup>2</sup>. As a consequence, the general relation for the electrostatics of the MOS structure derived in Eq. 8.9 applies here for a total potential difference that is given by  $\phi_{bi} + V$ :

$$\phi_{bi} + V = \phi_s(V) - \frac{Q_s(V)}{C_{ox}}$$

(8.18)

where, in general, we note that  $\phi_s$  and  $Q_s$  now depend on V.

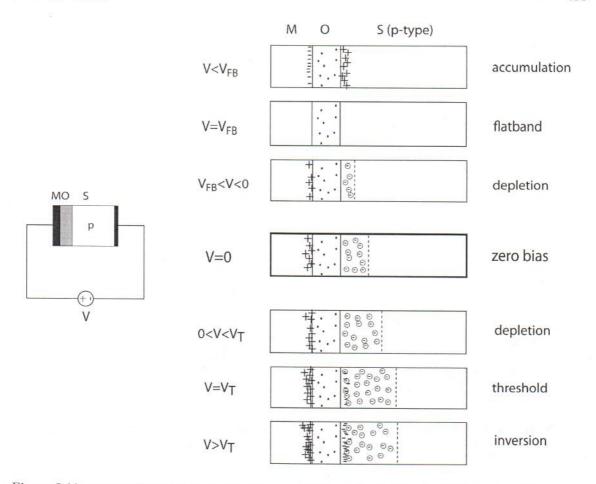

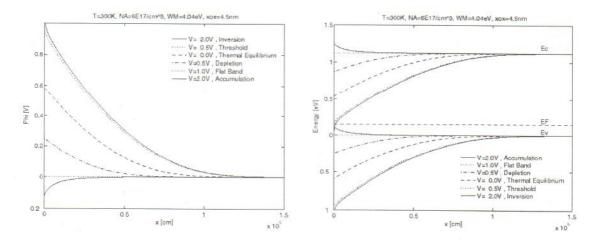

Let us now qualitatively discuss the changes that take place in the electrostatics of a MOS structure as a result of the application of a voltage. A pictorial view is sketched in Fig. 8.11. The center diagram shows the structure at zero bias in which a depletion region exists in the semiconductor. An identical amount of positive charge resides at the metal-oxide interface. If a negative voltage is applied, the potential difference across the structure is reduced. In consequence, the magnitude of the charge dipole must decrease. This implies that the depletion layer shrinks. This voltage regime in which the depletion region thickness is being modulated by the applied bias is referred to as **depletion**.

For sufficient negative bias, the potential difference across the structure is wiped out. This calls for the charge dipole to disappear and the depletion region to completely collapse. This condition is called **flatband**. If a more negative voltage than this is applied, the potential difference across the structure reverses sign. This now demands the appearance of positive charge in the semiconductor and a negative sheet of charge at the metal-oxide interface. This can only be accomplished by accumulating holes against the oxide-semiconductor interface, a condition that is referred to as **accumulation**. This is shown in the top diagram of Fig. 8.11.

Moving downwards from V=0 now, if a positive voltage is applied to the gate with respect to the semiconductor, the total potential difference across the structure increases and the depletion region has to widen to satisfy the electrostatics. If the voltage is made sufficiently large, eventually electrons start piling up at the insulator/semiconductor interface. The onset of this phenomenon is called **threshold**. For voltages higher than this, the electron concentration at the oxide-semiconductor interface becomes significant, a condition that is known as **inversion**. This is the regime that is exploited in MOSFETs.

<sup>&</sup>lt;sup>2</sup>In the Schottky junction and the PN junction, we assumed that the electrostatics under bias were identical to equilibrium even though current was flowing by. In most cases, this assumption gives reasonable results. In the case of the MOS structure, this assumption is particularly well justified since no current flows.

Figure 8.11: Impact of the application of a voltage to the charge distribution of a MOS structure. For negative voltages of the metal with respect to the semiconductor, the depletion region shrinks. For a large enough negative voltage, the structure is driven into accumulation. For positive voltages, the depletion region widens. For large enough voltage, the structure is driven into inversion.

We proceed to analyze these different situations in more detail in the following subsections.

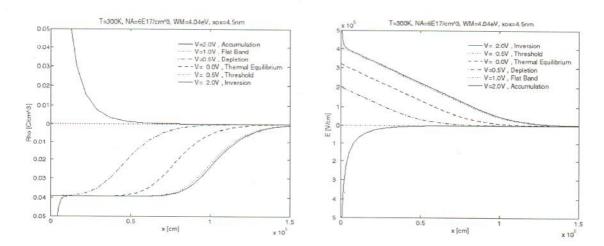

## 8.4.1 Depletion

A detailed view of the MOS electrostatics in the depletion regime is shown in Fig. 8.12. Starting with the potential distribution, the application of a voltage to the gate with respect to the body changes the potential difference across the MOS structure. This requires a modulation of the charge distribution. For V > 0, the potential difference increases from the zero bias value of  $\phi_{bi}$  to  $\phi_{bi} + V$ . In consequence, the depletion region widens and the electric field everywhere increases. For V < 0, the contrary happens and the potential difference is reduced, the depletion region shrinks and the electric field is lowered throughout.

The situation is well reflected in the evolution of the energy band diagram, which is also shown

Figure 8.12: From top to bottom and left to right: sketches of volume charge density, electric field, electrostatic potential, carrier concentration and energy band diagram of a MOS structure under zero bias and for bias negative and positive but close to zero (depletion regime).

in Fig. 8.12. For V>0, the Fermi level in the metal is pulled down with respect to the Fermi level in the semiconductor. As a result, the band bending across the oxide and the semiconductor increases. The contrary happens for V<0. Note how the Fermi level in the semiconductor is drawn flat and that the hole and electron quasi-Fermi levels overlap. This reflects the absence of current through the structure and the consideration that the semiconductor remains in a quasi-equilibrium state.

It is interesting to reflect on what happens to the carrier concentrations. This is sketched in the top right of Fig. 8.12. For V>0, the hole concentration drops close to the semiconductor/oxide interface as the depletion region widens. The contrary happens when V<0. Since the pn product has to remain constant (consistent with zero current), for V>0, the electron concentration close to the oxide/semiconductor interface rises while it drops for V<0.

In the depletion regime, the change in the potential build up across the structure modulates the depletion region thickness. Nevertheless, the essential character of the electrostatics remains unchanged from the situation that we discussed under zero bias. In consequence, an analytical description of the depletion regime can be obtained simply by going to our zero bias results and substituting  $\phi_{bi}$  by  $\phi_{bi} + V$ .

In particular, going back to the results obtained in Sec. 8.3.2, the depletion region thickness as a function of V is given by:

$$x_d(V) \simeq \frac{\epsilon_s}{C_{ox}} \left( \sqrt{1 + 4\frac{\phi_{bi} + V}{\gamma^2}} - 1 \right)$$

(8.19)

The total charge in the depletion region, from Eq. 8.10, can be written as:

$$Q_s(V) = Q_d(V) \simeq -\frac{1}{2}\gamma^2 C_{ox}(\sqrt{1 + 4\frac{\phi_{bi} + V}{\gamma^2}} - 1)$$

(8.20)

where we have used the definition of  $\gamma$  in Eq. 8.16.

The evolution of the surface potential with V can be easily obtained from Eq. 8.13:

$$\phi_s(V) \simeq \frac{1}{4}\gamma^2 (\sqrt{1 + 4\frac{\phi_{bi} + V}{\gamma^2}} - 1)^2$$

(8.21)

Similar relations can be obtained for any other variable of interest by starting from the zero bias equations derived in Sec. 8.3.2.

Exercise 8.3: Consider an MOS structure identical to that of Exercise 8.2 except for the use of a poly-Si gate ( $W_M = 4.04 \text{ eV}$ ). Calculate  $Q_s$  and its extent into the semiconductor for V = -0.5 V.

Let us assume that for V=-0.5~V this structure is in depletion (we will verify this in Exercise 8.4). The first step is to compute  $\phi_{bi}$  as in Exercise 8.2. This yields  $\phi_{bi}=1.0~V$ .  $Q_s$  can be obtained from Eq. 8.20 (the values of  $C_{ox}=7.7\times10^{-7}~F/cm^2$ , and  $\gamma=0.58~V^{1/2}$  were also obtained in Exercise 8.2):

$$Q_s = -\frac{1}{2}\gamma^2 C_{ox} \left(\sqrt{1 + 4\frac{\phi_{bi} + V}{\gamma^2}} - 1\right)$$

$$= -\frac{1}{2}(0.58)^2 V \times 7.7 \times 10^{-7} F/cm^2 \left[\sqrt{1 + 4\frac{(1.0 - 0.5) V}{(0.58 V)^2}} - 1\right] = -2.1 \times 10^{-7} C/cm^2$$

The extent of the depletion region is simply:

$$x_d = \frac{Q_s}{-qN_A} = \frac{-2.1 \times 10^{-6} \ C/cm^2}{-1.6 \times 10^{-19} \ C \times 6 \times 10^{17} \ cm^{-3}} = 22 \ nm$$

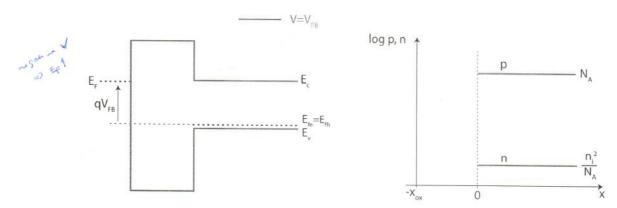

## 8.4.2 Flatband

For large enough negative voltage applied to the gate with respect to the body of the MOS structure, the depletion region is wiped out. This is referred to as flatband. In this instance, the potential build up across the structure is precisely zero. As a result, there is no charge dipole,

Figure 8.13: Energy band diagram and carrier concentration distribution in the MOS structure at flatband.

and there is no electric field anywhere. As sketched in Fig. 8.13, the energy bands are perfectly flat, hence the name, and the carrier concentrations are constant throughout the semiconductor which is then perfectly charge neutral.

The voltage required to drive the structure to flatband is referred to as the flatband voltage. Since there is no charge in the semiconductor,  $Q_s = 0$ . As a result, the band bending is zero and the surface potential  $\phi_s = 0$ . Then, from the general relation for electrostatics in Eq. 8.18, the flatband voltage is given by:

$$V_{FB} = -\phi_{bi} \tag{8.22}$$

Looking back at the expression of  $\phi_{bi}$  given in Eq. 8.1, it is clear that the flatband voltage is entirely set by the bulk properties of the metal and the semiconductor.

The flatband voltage is an important reference voltage in the operation of MOS devices. We will extensively use it in the treatment of the MOS structure and in the analysis of MOSFETs.

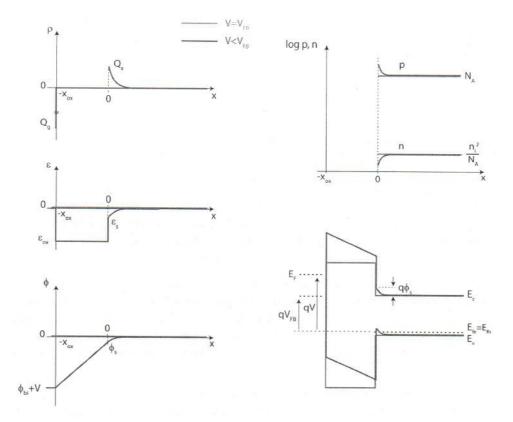

### 8.4.3 Accumulation

Nothing prevents us from applying a voltage across the MOS structure that is more negative than  $V_{FB}$ . When this is done, the gate is placed at a more negative potential than the body of the semiconductor. This forces a charge dipole with positive charge in the semiconductor and an identical amount of negative charge at the metal-oxide interface. Positive charge on the semiconductor can be obtained if the hole concentration is higher than the acceptor concentration. Since holes are mobile, they will tend to pile up, or accumulate, at the oxide-semiconductor interface. This is the accumulation regime.

A detailed view of the electrostatics in accumulation is shown in Fig. 8.14. The thin hole accumulation layer is imaged at the gate-oxide interface where there is a negative sheet of charge. This yields electric field and electrostatic potential distributions as sketched in the figure and a band structure that now bends upwards towards the metal.

Figure 8.14: From top to bottom and left to right: sketches of volume charge density, electric field, electrostatic potential, carrier concentration and energy band diagram of a MOS structure at flatband and in accumulation.

It is relatively straightforward to derive first-order expressions for the hole accumulation charge and other electrostatic parameters under the *sheet-charge approximation*. This assumes that the accumulation layer is much thinner than any other dimensions in the structure. The hole distribution in the semiconductor reflects a balance between drift and diffusion. Hence, its extent is expected to be of the order of the Debye length, which can be quite small.

Under the sheet charge approximation, the surface potential in accumulation is:

$$\phi_s \simeq 0 \tag{8.23}$$

This is because a sheet of charge produces a sharp change in the electric field over zero distance and this does not accrue any potential buildup.

If we denote as  $Q_a$  the sheet hole charge density in the accumulation layer, then, using Eq. 8.18, we can easily obtain:

$$Q_a \simeq C_{ox}(V_{FB} - V) \tag{8.24}$$

where we have also used Eq. 8.22. This is an important result. Once in accumulation, the hole accumulation charge increases linearly with the voltage that is applied beyond the flatband voltage.

## 8.4.4 Threshold

We now come back to applying positive voltages to the gate with respect to the body. As we discussed above, for V>0, the depletion region in the semiconductor widens. This is necessary to accommodate the additional negative charge required to satisfy the higher external potential difference between the gate and the body (see Fig. 8.12). A consequence of this can also be seen in this figure and that is that the electron concentration at the surface of the semiconductor increases. This is also reflected in the energy band diagram in which we see that as a result of the increased band bending associated with the enlarged depletion region, the conduction band edge at the surface of the semiconductor gets closer to the Fermi level.

It is clear that there is a voltage for which the electron concentration at the surface becomes equal to the hole concentration in the body of the semiconductor (see Fig. 8.15). This conditions is called threshold and it marks the onset of the inversion regime. "Threshold" is a very appropriate name as at this voltage, the semiconductor type changes at the surface from p-type to n-type. For gate voltages more positive than the threshold voltage, the electrostatics of the MOS structure drastically change in character.

It is relatively straightforward to derive an expression for the threshold voltage of a MOS structure. We start by finding an expression for the surface potential at threshold,  $\phi_{sT}$ . For this, we can use the Boltzmann relation and relate the difference in electrostatic potential between the surface and the bulk, precisely  $\phi_{sT}$ , to the ratio of electron concentration at these two locations. This yields:

$$\phi_{sT} = \frac{kT}{q} \ln \frac{n(x=0)|_T}{\frac{n_s^2}{N_A}} = 2\frac{kT}{q} \ln \frac{N_A}{n_i} = 2\phi_f$$

(8.25)

where we have taken  $n(x=0)|_T = N_A$ . We discuss the meaning of  $\phi_f$  below.

We next need an expression for the charge in the semiconductor at threshold. If we can neglect the contribution from the electrons at the surface (not a bad assumption since the depletion region is much thicker than this thin electron layer), then the semiconductor charge at threshold is associated with the depletion region. For reasons that will become clear soon, we denote the thickness of the depletion region at threshold as  $x_{dmax}$  and the depletion charge as  $Q_{dmax}$ . With a potential build up across the depletion layer of  $\phi_{sT}$ , using Eq. 8.17,  $x_{dmax}$  and  $Q_{dmax}$  are, respectively, given by:

$$x_{dmax} \simeq \sqrt{\frac{2\epsilon_s \phi_{sT}}{qN_A}}$$

(8.26)

and

Figure 8.15: From top to bottom and left to right: sketches of volume charge density, electric field, electrostatic potential, carrier concentration and energy band diagram of a MOS structure at zero volts, in depletion regime and at threshold.

$$Q_{dmax} \simeq -\sqrt{2\epsilon_s q N_A \phi_{sT}} \tag{8.27}$$

We can now use the general relation for electrostatics of the MOS structure (Eq. 8.18) at threshold to obtain:

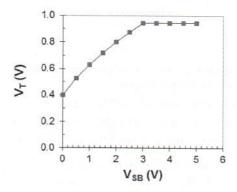

$$V_T = -\phi_{bi} + \phi_{sT} - \frac{Q_{dmax}}{C_{ox}} = V_{FB} + \phi_{sT} + \gamma \sqrt{\phi_{sT}}$$

$$\tag{8.28}$$

where we have also substituted Eqs. 8.22, 8.27 and 8.16.

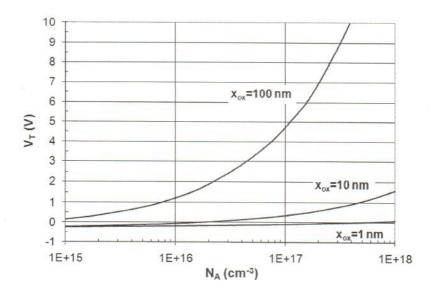

$V_T$  is the threshold voltage of the MOS structure and it plays a key role in MOSFET operation.  $V_T$  depends on all the key parameters of the MOS structure: semiconductor doping level, oxide thickness and gate work function. Fig. 8.16 shows  $V_T$  as a function of  $N_A$  and  $x_{ox}$  for a n<sup>+</sup>-polySi gate and SiO<sub>2</sub> dielectric. As  $N_A$  or  $x_{ox}$  increase, so does  $V_T$ . Notice that the dependence on doping is much weaker for thin oxides. This is because the doping dependence of  $V_T$  is mainly through the square root doping dependence of  $\gamma$  (Eq. 8.16). For a thin oxide,  $C_{ox}$  is high, and as Eq. 8.16 shows, the absolute magnitude of  $\gamma$  is very small.

Figure 8.16: Threshold voltage,  $V_T$ , vs. substrate doping level for different values of the oxide thickness. The gate is made out of n<sup>+</sup>-polySi ( $W_M = 4.04 \ eV$ ) and the oxide is SiO<sub>2</sub>.

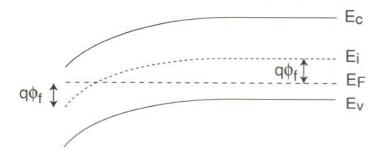

Figure 8.17: Energy band diagram of semiconductor at the onset of inversion (p-substrate). The definition of  $\phi_f$  is indicated.

In Eq. 8.25, the surface potential at threshold was defined in terms of  $\phi_f$ . Fig. 8.17 illustrates this definition.  $\phi_f$  is the distance in energy between the intrinsic Fermi level and the Fermi level in the body of the semiconductor. When the band bending in the semiconductor is precisely equal to  $2\phi_f$ , then the electron concentration at the surface is identical to the hole concentration in the bulk.

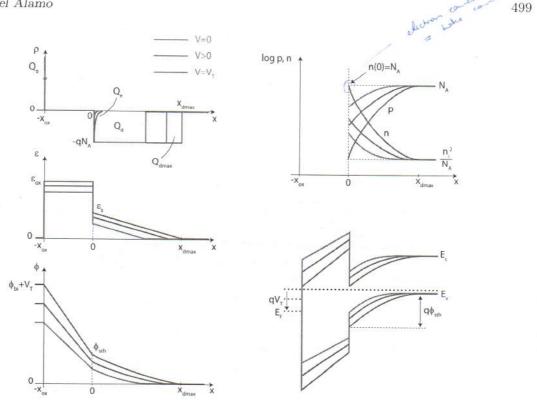

### 8.4.5 Inversion

Threshold marks the onset of the creation of an inversion layer of electrons at the oxide-semiconductor interface of a MOS structure. This does not occur abruptly at the treshold voltage but for  $V > V_T$  its existence can no longer be ignored. In fact, for  $V > V_T$  the electrostatics of the MOS structure are profoundly affected by the presence of this inversion layer.

Applying a gate voltage that exceeds  $V_T$  demands an increase in the magnitude of the charge dipole across the MOS structure. To understand what this implies on the semiconductor side, we need to note the dependences of the inversion layer charge,  $Q_i$ , and depletion region charge,  $Q_d$ , on the surface potential. While  $Q_i$  is expected to increase exponentially with  $\phi_s$  (more on this later),  $Q_d$  evolves as the square root of  $\phi_s$  (Eq. 8.17). Hence, any increase in  $\phi_s$  brought about by an increase in voltage will mostly grown the inversion layer while it will only produce a minor increase in the depletion region thickness beyond its value at threshold. It is because of this that we denote the thickness and charge associated with the depletion region at threshold as  $x_{dmax}$  and  $Q_{dmax}$ , respectively.

Fig. 8.18 illustrates the electrostatics of the MOS structure at threshold and in inversion. Starting from the top-right sketch, in inversion the electron concentration at the surface of the semiconductor increases in a prominent way. This is more clearly seen in the top-left sketch that shows the charge distribution across the structure. In inversion, the electron concentration at the surface exceeds the background acceptor concentration. As a result of the appearance of the inversion layer, the electric field exhibits a rather abrupt jump at the semiconductor surface. However, since the inversion layer is expected to be very thin (the electrons are "jammed" against the oxide), the electrostatic potential does not change very much. Due to the exponential dependence on  $Q_i$  on  $\phi_s$ , not much of a change in  $\phi_s$  is needed to induce the required amount of  $Q_i$  to satisfy the electrostatics. This is also reflected in the band diagram on the bottom right which shows a band bending across the semiconductor that has not changed much beyond threshold with most of the extra applied gate voltage used to bend the bands across the oxide.

It is relatively straightforward to obtain a first-order expression for the evolution of the inversion charge with the gate voltage. This can easily be done under the context of the *sheet-charge approximation*. As in accumulation, we assume that the inversion layer charge is very thin in the scale of the other dimensions of the problem  $(x_{ox} \text{ and } x_{dmax})$ . Under this approximation, the surface potential in inversion is approximately equal to the value that it has at threshold:

$$\phi_s \simeq \phi_{sT} \tag{8.29}$$

We can now use the general relation for the electrostatics of the MOS structure (Eq. 8.18) in inversion:

$$\phi_{bi} + V = \phi_{sT} + \frac{Q_{dmax} + Q_i}{C_{ox}} \tag{8.30}$$

We now solve for  $Q_i$  and substitute the expressions of  $V_{FB}$  (Eq. 8.22) and  $V_T$  (Eq. 8.28) to get:

$$Q_i = -C_{ox}(V - V_T) \qquad \text{for } V \ge V_T \tag{8.31}$$

This is a very important equation. It is often called the *charge-control relation of the inversion layer*. It states that once reached threshold, the application of additional voltage across the MOS structure grows the inversion layer charge in a linear manner.

Figure 8.18: From top to bottom and left to right: sketches of volume charge density, electric field, electrostatic potential, carrier concentration and energy band diagram of a MOS structure at zero volts, at threshold and in inversion.

While we have obtained important and useful results using a simple view of the electrostatics of the MOS structure, a more rigorous analysis is often desirable. Advanced Topic AT8.1 at the end of this chapter presents the so-called Poisson-Boltzmann formulation of the MOS electrostatics. This approach yields more accurate analytical models for many important aspects of the MOS electrostatics.

Exercise 8.4: Consider an MOS structure identical to the one studied in Exercise 8.3. Compute  $V_T$  and  $Q_i$  for V = 2 V.

503

We use results obtained for  $\phi_{bi}$ ,  $C_{ox}$ , and  $\gamma$  from Exercise 8.3. The first step is to compute  $\phi_{sT}$  using Eq. 8.25:

$$\phi_{sT} = 2\frac{kT}{q} \ln \frac{N_A}{n_i} = 2 \times 0.026 \times \ln \frac{6 \times 10^{17}}{1.02 \times 10^{10}} = 0.93 \ V$$

We then use Eq. 8.28 to obtain  $V_T$ :

$$V_T = V_{FB} + \phi_{sT} + \gamma \sqrt{\phi_{sT}} = -1.0 \ V + 0.93 \ V + 0.58 \ V^{1/2} \times \sqrt{0.93 \ V} = 0.49 \ V$$

The calculation of  $Q_i$  is now straightforward through Eq. 8.31:

$$Q_i = -C_{ox}(V - V_T) = -7.7 \times 10^{-7} \ F/cm^2 \times (2 - 0.49 \ V) = -1.2 \times 10^{-6} \ C/cm^2$$

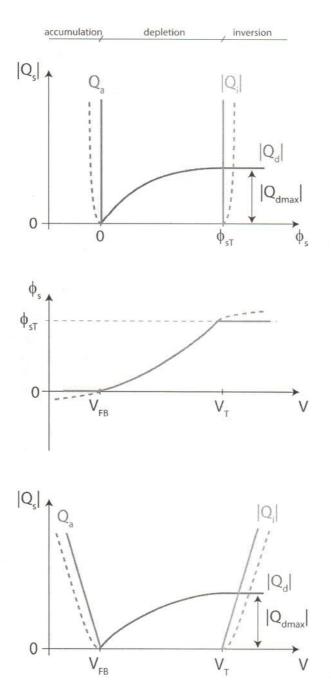

## 8.4.6 Summary of charge-voltage characteristics

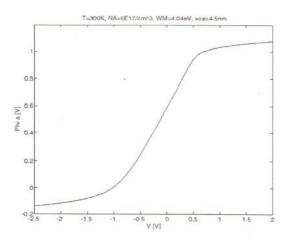

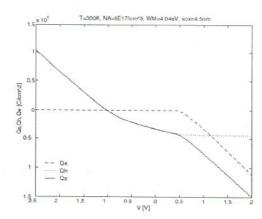

Figs. 8.19 summarizes the charge-voltage characteristics of the MOS structure discussed in this section. On the top, the absolute of the semiconductor charge is graphed against  $\phi_s$ . In the accumulation regime,  $Q_s = Q_a > 0$ . Under the sheet-charge approximation, in accumulation  $\phi_s \simeq 0$ . In depletion,  $Q_s = Q_d < 0$  and  $|Q_d|$  evolves in a square-root form with  $\phi_s$ . In inversion,  $Q_s = Q_{dmax} + Q_i < 0$ . Under the sheet-charge approximation,  $\phi_s \simeq \phi_{sT}$ .

The graph in the middle shows  $\phi_s$  vs. V. For  $V < V_{FB}$ , we have the accumulation regime with  $\phi_s \simeq 0$ . In depletion,  $\phi_s$  evolves with V according to Eq. 8.21. In inversion, for  $V > V_T$ ,  $\phi_s \simeq \phi_{sT}$ .

At the bottom of Fig. 8.19 the absolute of the semiconductor charge is graphed against the voltage. For  $V < V_{FB}$ , the structure is in accumulation and  $Q_s$  is linear on  $V_{FB} - V$ . Between  $V_{FB}$  and  $V_T$ , the structure is in depletion and the dependence of  $Q_s$  with V follows the square-root form given by Eq. 8.20. For  $V > V_T$ , the structure is in inversion and  $Q_i$  is linear on  $V - V_T$ .

In the simple model developed in this section, the use of the sheet-charge approximation "pins" the surface potential in accumulation and inversion at 0 and  $\phi_{sT}$ , respectively. In reality, carriers at the semiconductor surface are distributed in depth to some extent. This implies that  $\phi_s$  becomes slightly negative in accumulation and it also increases somehow past  $\phi_{sT}$  in inversion. This is indicated by the dashed lines in Fig. 8.19.

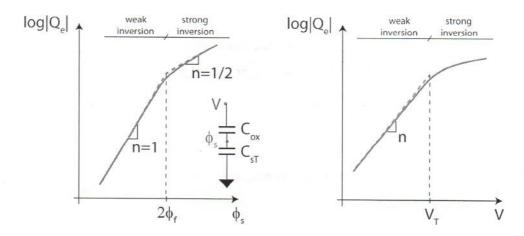

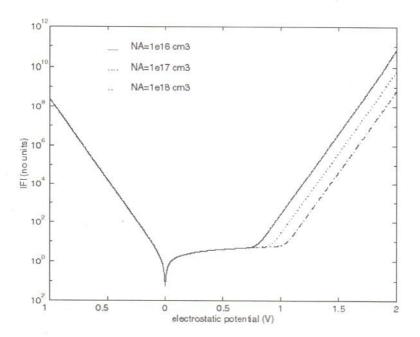

A more rigorous model that accounts for this is developed in Appendix AT8.1. This is referred to as the Poisson-Boltzmann formulation. This model does not make any assumptions about the spatial distribution of carriers at the semiconductor surface. It therefore yields a more accurate description of the electrostatics that yields, among other results, the evolution of carrier charge as a function of surface potential, and the surface potential vs. the applied voltage. These key results are summarized here.

In accumulation, the accumulation charge is found to depend on  $\phi_s$  according to the following

Figure 8.19: Summary of charge-voltage characteristics of MOS structure. Top: Semiconductor charge vs. surface potential. Middle: Surface potential vs. voltage. Bottom: Semiconductor charge vs. voltage. Dashed lines represent improved dependencies obtained from the Poisson-Boltzmann model of Appendix AT8.1.

expression (from Eq. 8.106):

$$Q_a \simeq \sqrt{2\epsilon_s kT N_A} \sqrt{\exp \frac{-q\phi_s}{kT} + \frac{q\phi_s}{kT} - 1} \qquad \text{for } \phi_s < 0$$

(8.32)

Notice how  $Q_a$  goes to zero, as  $\phi_s$  goes to zero. The leading term of  $Q_a$  for strong accumulation  $(|\phi_s| \gg kT/q)$  depends exponentially on  $-q\phi_s/2kT$ .

Another important result from the Poisson-Boltzmann formulation is the relationship between  $\phi_s$  and V. In accumulation, this is approximately (from Eq. 8.108):

$$\phi_s \simeq -\frac{kT}{q} \ln\{1 + \left[\frac{C_{ox}(V_{FB} - V)}{\sqrt{2\epsilon_s kT N_A}}\right]^2\} \qquad \text{for } V < V_{FB}$$

(8.33)

At flatband,  $\phi_s = 0$ , but as  $V < V_{FB}$ ,  $\phi_s$  becomes negative but it does so quite slowly.

In inversion, the dependence of  $Q_i$  on  $\phi_s$  is found to be (from Eq. 8.119):

$$Q_i \simeq -\sqrt{2\epsilon_s kT N_A} \left[ \sqrt{\frac{q2\phi_f}{kT} + \exp\frac{q(\phi_s - 2\phi_f)}{kT} - 1} - \sqrt{\frac{q2\phi_f}{kT}} \right] \qquad \text{for } \phi_s > 2\phi_f$$

(8.34)

In this expression,  $Q_i$  goes to zero as  $\phi_s$  approaches  $2\phi_f$ . In strong inversion, the leading term of  $Q_i$  goes as  $\sim \exp(q\phi_s/2kT)$ .

The dependence of  $\phi_s$  on V is given by (from Eq. 8.122):

$$\phi_s \simeq 2\phi_f + \frac{kT}{q} \ln\{\left[\frac{C_{ox}(V - V_T)}{\sqrt{2\epsilon_s kT N_A}} - \sqrt{\frac{q2\phi_f}{kT}}\right]^2 - \frac{q2\phi_f}{kT} + 1\}$$

for  $V > V_T$  (8.35)

At  $V = V_T$ ,  $\phi_s = 2\phi_f$ , consistent with our definition of threshold. In inversion,  $\phi_s$  does increase somehow above  $2\phi_f$  but it does so in a logarithmic way.

Other interesting results for the MOS electrostatics under the Poisson-Boltzmann formulation are derived in Appendix AT8.1.

# 8.5 Dynamics of the MOS structure

A MOS structure looks in many ways like a capacitor. On one side there is a metal plate; on the other side there is the semiconductor which is in effect another conducting "plate". In the middle, there is a dielectric, the oxide. Depending on the voltage that is applied to the MOS structure, net electrical charge exists at the metal/dielectric interface and in the semiconductor.

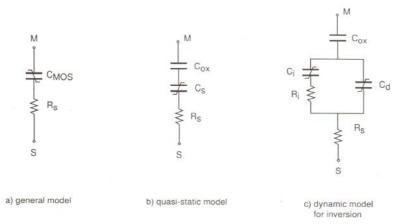

Figure 8.20: Equivalent circuit models for the MOS structure: a) general model; b) quasi-static model; c) dynamic model for inversion.

The total charge at these two plates is of equal magnitude but opposite sign. If the voltage is changed, the charge on both plates is modified by the same amount in absolute terms. At all times, the magnitude of the charge on each plate is identical. The MOS structure behaves as a true capacitor. A simple equivalent model description of the MOS structure consists then of a capacitor, capturing the MOS electrostatics, in series with a resistor that accounts for the finite conductance of the substrate. This is sketched on the left of Fig. 8.20. This simple equivalent circuit provides a reasonable description of the dynamics of the MOS structure.

For the simple RC circuit of the left of Fig. 8.20 to be useful, all the dependencies of the MOS capacitance need to be properly described. There are two critical dependences to understand and represent. The first one is the impact of voltage. The second one, perhaps less obvious, is time or the dynamic behavior of the electrostatics themselves. We study these two factors separately in the next two subsections.

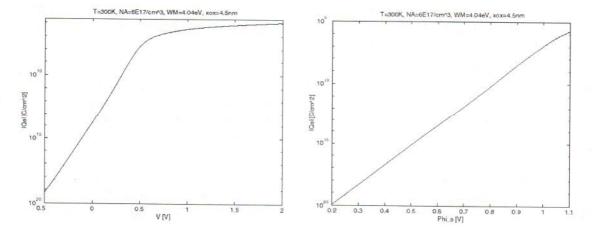

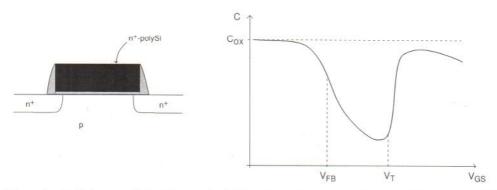

## 8.5.1 Quasi-static C-V characteristics

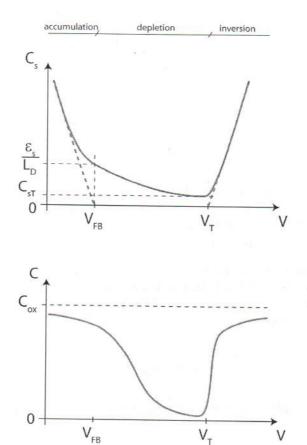

The capacitance-voltage characteristics of an MOS structure have tremendous practical importance as a diagnostic tool. From the C-V characteristics, one can extract the flat-band voltage, the threshold voltage, the oxide thickness and the semiconductor doping level. Also a detailed study of the C-V characteristics can reveal non-idealities in the structure such as mobile oxide charge, interface states, or gate doping depletion (in the case of a polySi gate). The capacitance-voltage characteristics of a MOS structure are also of capital importance in just about any of its applications. The C-V characteristics summarize the complex behavior of the MOS structure that was described in detail in the preceding sections. Studying in detail the C-V characteristics is an opportunity to review and solidify our understanding of the physics of the MOS structure.

As we have encountered before in this book, a quasi-static situation is one without significant memory effects. Effectively, at all times, the MOS structure behaves as if it was in DC. The term quasi-static C-V characteristics refers to the capacitance that is measured at a certain bias

voltage in a small-signal configuration when the frequency of the driving signal is low enough for the electrostatics to be independent of frequency (how small the frequency needs to be will become clear later). The formalism of the electrostatics of the MOS structure described so far in this chapter completely applies to a quasi-static situation and is therefore the basis for a derivation of the quasi-static C-V characteristics.

A general definition of capacitance of the MOS structure is the change of charge on the gate as a result of a small change in voltage across the structure:

$$C = \frac{dQ_g}{dV} \tag{8.36}$$

Since  $Q_g = -Q_s$ , using the chain rule for derivatives, the capacitance can be expressed as:

$$C = -\frac{dQ_s}{dV} = -\frac{dQ_s}{d\phi_s} \frac{1}{\frac{dV}{d\phi_s}}$$

(8.37)

From the general relationship 8.18, we have:

$$\frac{dV}{d\phi_s} = 1 - \frac{1}{C_{ox}} \frac{dQ_s}{d\phi_s} \tag{8.38}$$

Let us define the semiconductor capacitance,  $C_s$ , as:

$$C_s = -\frac{dQ_s}{d\phi_s} \tag{8.39}$$

As we will see below,  $C_s$  defined this way is always positive. Armed with this definition, Eq. 8.38 can be rewritten as:

$$\frac{dV}{d\phi_s} = 1 + \frac{C_s}{C_{crr}} \tag{8.40}$$

Substituting this in Eq. 8.37, we get:

$$C = \frac{1}{\frac{1}{C_{ox}} + \frac{1}{C_{s}}} \tag{8.41}$$

There is a simple physical interpretation to the result embodied in Eqs. 8.39 and 8.41. The capacitance of the MOS structure can be thought of as two capacitances in series, one associated with the oxide,  $C_{ox}$ , and another one associated with the semiconductor  $C_s$ . The definition of  $C_s$  of Eq. 8.39 is consistent with this interpretation since it represents the change of the charge in the semiconductor as a result of a change in the electrostatic potential build-up across the semiconductor. This simple picture of two capacitors in series is schematically illustrated at the center of Fig. 8.20.

We now derive first-order expressions for  $C_s$  in the various regimes. In accumulation,  $Q_s = Q_a$ . Eq. 8.32 gives  $Q_a$  vs.  $\phi_s$ . From this, we can easily derive  $C_s$  in accumulation. For strong accumulation ( $|\phi_s| \gg kT/q$ ), we find:

$$C_s = -\frac{dQ_a}{d\phi_s} \simeq \frac{q}{2kT} C_{ox} (V_{FB} - V) \qquad \text{for } V < V_{FB}$$

(8.42)

where we have used Eq. 8.24. In strong accumulation,  $C_s$  increases linearly with the gate voltage below flatband.

Close to flatband, when  $\phi_s \simeq 0$ , the semiconductor capacitance is:

$$C_s = -\frac{dQ_a}{d\phi_s} \simeq \frac{\epsilon}{L_D}$$

for  $V \simeq V_{FB}$  (8.43)

where  $L_D$  is the Debye length. This is a particularly intuitive result since we know that the Debye length gives a sense of the distance over which small perturbations to charge neutrality in an extrinsic semiconductor are screened out.

In depletion,  $Q_s = Q_d$ . The dependence of the depletion charge with  $\phi_s$  is given by Eq. 8.17. Using also the dependence of  $\phi_s$  on V given by Eq. 8.21 and the definition of  $\gamma$  in Eq. 8.16, we can obtain:

$$C_s = -\frac{dQ_d}{d\phi_s} \simeq \frac{C_{ox}}{\sqrt{1 + 4\frac{V - V_{FB}}{\gamma^2}} - 1}$$

for  $V_{FB} < V < V_T$  (8.44)

This expression for the semiconductor capacitance in depletion can also be obtained if we realize that:

$$C_s \simeq \frac{\epsilon_s}{x_d}$$

for  $V_{FB} < V < V_T$  (8.45)

and we use the expression of  $x_d(V)$  given in Eq. 8.19. In the depletion region, there is a depletion region underneath the oxide. When the surface potential changes, the edge of the depletion region moves. This is at a distance  $x_d$  away from the semiconductor/oxide interface.

Looking at the Poisson-Boltzmann formulation in Appendix AT8.1, Eq. 8.44 is only valid for  $\phi_s \gg kT/q$  or with V not to close to  $V_{FB}$ . As V goes to zero, this equation cleearly diverges. Using the more rigorous model of Appendix AT8.1, we can easily find that in the depletion regime for V close to zero, the semiconductor capacitance approaches the value given by Eq. 8.43.

In inversion,  $Q_s = Q_i$ . Eq. 8.34 gives the dependence of  $Q_i$  on  $\phi_s$ . We also use Eq. 8.31 to get:

$$C_s = -\frac{dQ_i}{d\phi_s} \simeq \frac{q}{2kT} Q_i = \frac{q}{2kT} C_{ox} (V - V_T) \qquad \text{for } V > V_T$$

(8.46)

Figure 8.21: Top: Sketch of semiconductor capacitance of MOS structures in different regimes. Bottom: Overall MOS capacitance vs. voltage.

The evolution of the semiconductor capacitance with V is show at the top of Fig. 8.21. In accumulation and inversion,  $C_s$  increases in a linear fashion with V. In depletion, it evolves in a square-root form. The minimum capacitance is obtained around threshold.

The overall MOS capacitance is obtained by inserting these expressions for  $C_s$  into Eq. 8.41. In accumulation, we have:

$$C \simeq C_{ox} \frac{1}{1 + \frac{2kT}{q(V_{FB} - V)}} \qquad \text{for } V < V_{FB}$$

$$\tag{8.47}$$

Around flatband, we get:

$$C \simeq C_{ox} \frac{1}{1 + C_{ox} \frac{\epsilon_s}{L_D}}$$

for  $V \simeq V_{FB}$  (8.48)

In depletion, we obtain:

$$C \simeq \frac{C_{ox}}{\sqrt{1 + 4\frac{V - V_{FB}}{\gamma^2}}} \qquad \text{for } V_{FB} < V < V_T$$

$$\tag{8.49}$$

In inversion, we get:

$$C \simeq C_{ox} \frac{1}{1 + \frac{2kT}{q(V - V_T)}} \qquad \text{for } V > V_T$$

(8.50)

The bottom of Fig. 8.21 sketches C vs. V. Since we are looking at two capacitances in series, the smaller one tends to dominate. Hence, under strong accumulation and inversion, the overall MOS capacitance approaches  $C_{ox}$ . In depletion,  $C_s$  decreases as V increases beyond  $V_{FB}$ , and the overall capacitance can become quite small.

The capacitance of the semiconductor in the depletion regime at threshold is of special significance as it enters in models for the subthreshold behavior of the MOS structure which we study below. An expression for this can be obtained from Eq. 8.44 by setting  $V = V_T$ . After some algebra, this can be written as:

$$C_{sT} \simeq C_{ox} \frac{\gamma}{2\sqrt{2\phi_f}} \tag{8.51}$$

This result can also be obtained if we realize that  $C_{sT} = \epsilon_s/x_{dmax}$  and use the expression for  $x_{dmax}$  in Eq. 8.26.

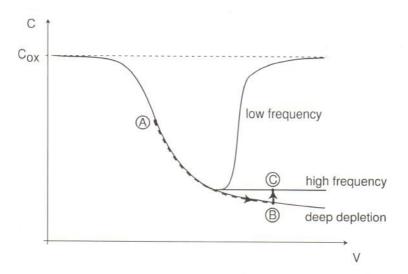

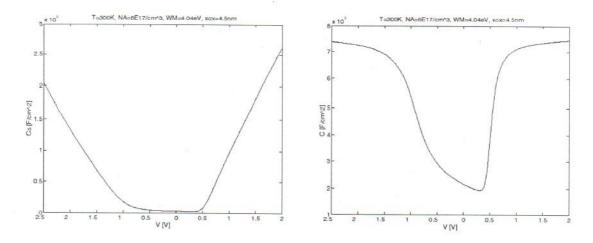

# 8.5.2 High-frequency C-V characteristics

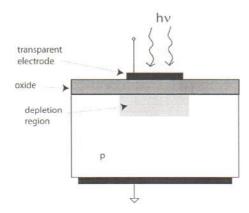

The quasi-static C-V characteristics described above are obtained for a driving signal with lowenough frequency. If a high frequency is employed, the physics change. This is described in this section. Let us examine the three voltage regimes separately.

The application of an AC voltage modulates the charge in the semiconductor. In the accumulation regime, this charge is made out of holes in the accumulation layer. Since holes are majority carriers in the semiconductor, they are in good communication with the outside world through the ohmic contact. The proper time constant to get holes in and out of the accumulation layer is the dielectric relaxation time of the substrate or the RC time constant of the whole structure, whichever is largest. Either case, it is a rather fast phenomenon. In consequence, the C-V characteristics in accumulation derived in the previous section apply up to fairly high frequencies. The situation is identical in depletion, where the hole concentration is modulated at the edge of the depletion region in response to the application of an AC voltage. The C-V characteristics in depletion obtained above also apply up to rather high frequencies.

The situation is quite different in inversion. As we discussed above, in strong inversion, the electron concentration in the inversion layer is modulated in response to the AC voltage. The thickness of the depletion region is basically unchanged. The extra electrons required to satisfy

Figure 8.22: Illustration of change in charge in semiconductor in response to an AC voltage signal at low frequencies and high frequencies.

the electrostatics have to be generated in the semiconductor. The proper time constant for this is the generation lifetime, typically in the  $\mu s-ms$  range. In consequence, the C-V characteristics derived above only apply if the AC signal changes slowly in the scale of the inverse of  $\tau_g$ , this typically means frequencies in the kHz range or below. For higher frequencies, the inversion capacitance picture ought to look quite different from what has been discussed so far.

In fact, if the frequency is high enough, the electron concentration in the inversion layer is unable to respond to the AC voltage signal. Since the voltage is nevertheless changing, charge modulation must take place somewhere to satisfy the electrostatics. The only other place where charge can be modulated is at the edge of the depletion region with the substrate. This can be accomplished by getting holes in and out of the substrate through the ohmic contact, a process that as we discussed above, is limited by the RC time constant of the structure. This is sketched in Fig. 8.22.

This understanding allows us to conclude that the high-frequency inversion semiconductor capacitance is, to the first order, equal to the depletion capacitance at threshold (derived in Eq. 8.51):

$$C_{s,HF} \simeq C_{sT} \tag{8.52}$$

This is because in inversion  $\phi_s \simeq \phi_{sT}$  and  $x_d \simeq x_{dmax}$ .  $C_{sT}$  can be a substantially lower value than the quasi-static capacitance of the structure for the same bias point (given by Eq. 8.46).

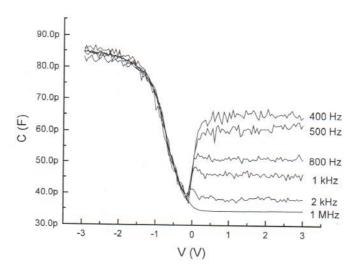

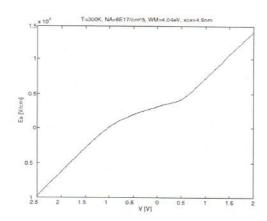

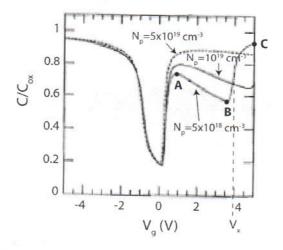

A comparison of the theoretical C-V characteristics of a typical MOS structure at low-frequency and high frequency is shown in Fig. 8.23. In inversion, C remains at the lowest value

Figure 8.23: C-V characteristics of typical MOS structure at low-frequency (quasi-static), high frequency, and under a fast ramp or after a step (deep depletion). The marked points refer to the transient described in Fig. 8.25.

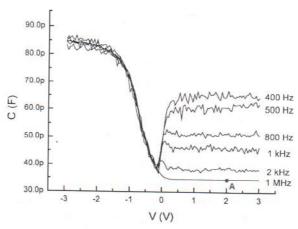

attained at threshold. Experimental results showing the evolution of the C-V characteristics of a typical MOS with frequency are depicted in Fig. 8.24.

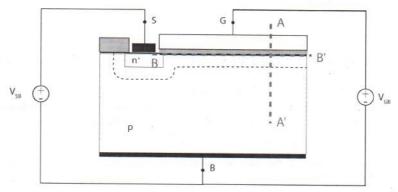

An equivalent circuit description of the high frequency behavior of the MOS structure is shown on the right of Fig. 8.20. In this model, we have broken the semiconductor capacitance in two capacitors in parallel: one associated with the depletion region  $C_d$ , and another one associated with the inversion layer  $C_i$ . In series with the inversion layer capacitance is a resistor  $R_i$ . This resistor captures the difficulty of providing electrons to the inversion layer. The  $R_i - C_i$  branch behaves as a low-pass filter. Its time constant,  $R_iC_i$ , is the inverse of the generation lifetime  $\tau_g$  that controls electron generation in the depletion region. For low frequencies, the impedance of this branch is dominated by  $C_i$ . Since it is in parallel but it is much larger than  $C_d$ , the capacitance of the MOS structure is approximately  $C_i$ . At high frequencies, on the other hand, the impedance is dominated by  $R_i$ . In consequence, the capacitance of the MOS structure is approximately  $C_d$ .

#### 8.5.3 Deep depletion

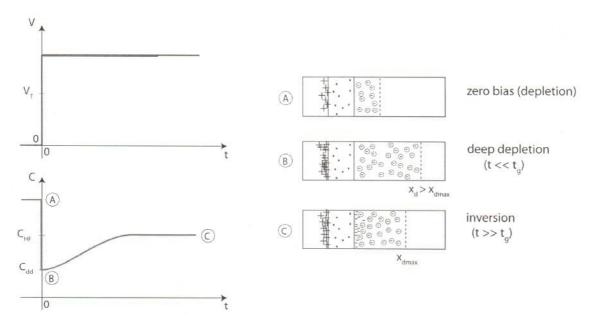

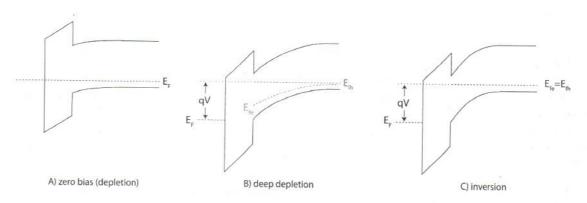

The previous section has revealed the rich dynamics of the MOS structure in the inversion regime that originate from the "sluggishness" of response of the inversion layer to changes in applied voltage. The condition just studied was one in which a small high-frequency signal was applied on top of a DC bias. Another dynamic situation of great interest is one that results when a MOS structure is suddenly switched into inversion by the application of a step or a fast voltage ramp. This condition is called deep depletion.

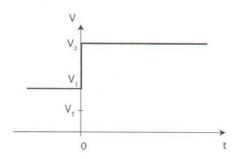

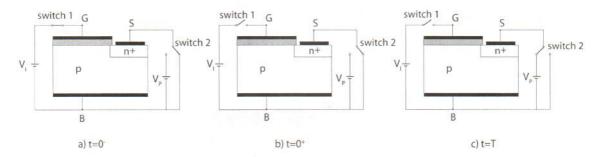

Consider a MOS structure at zero bias. Let us assume that at V = 0 it is in depletion. Let us consider what happens if at t = 0, we apply a voltage step, as sketched in Fig. 8.25. If the step

Figure 8.24: Experimental C-V characteristics of an MOS structure as a function of frequency. At low frequency, the measurement becomes noisy and in general it is not possible to obtain the ideal quasi-static behaviour sketched in Fig. 8.21 [courtesy of T. Payakapan, MIT].

is negative and of a magnitude that exceeds the flat-band voltage, the structure will be driven into accumulation. After an RC time constant, a relatively short time, the depletion region will be wiped out and holes will accumulate at the semiconductor/oxide interface. If the step is negative but of a magnitude smaller than  $V_{FB}$  or positive but smaller than  $V_T$ , the depletion region thickness will change. This also happens in a time scale of the corresponding RC time constant.

If the voltage step is positive and exceeds the threshold voltage, the situation gets complicated. A short time after the application of the step (following the inevitable RC delay), the only way to satisfy the electrostatics of the structure is for the depletion region to widen beyond  $x_{dmax}$ . This is because even though the voltage is such that an inversion layer should be formed, there has not been enough time for the electrons to be generated. For this to happen, we must wait a time of order of the generation lifetime,  $\tau_g$ , a fairly long time in the scale of many useful electronic functions. The MOS structure has gone into what is called "deep depletion" because for a while the depletion region thickness widens beyond the value that corresponds to the inversion regime. If the step has enough duration, eventually the required electrons will be generated, the inversion layer will be formed and the depletion region will collapse down to  $x_{dmax}$ . This is sketched in Fig. 8.25.

The dynamics of the deep depletion regime can be observed experimentally by measuring the capacitance of the MOS structure during the transient. This can be accomplished by overlapping a high-frequency sinusoidal signal on top of the voltage step. The result is sketched in Fig. 8.25. After the RC transitory has died off but before a significant amount of electrons has been generated, the capacitance in deep depletion will be lower than the high-frequency capacitance in the inversion regime. This is because  $x_d > x_{dmax}$ . Given enough time, the inversion layer will eventually grow, the depletion region will collapse back to  $x_{dmax}$  and the capacitance will revert